Documentazione e strumenti di supporto

La descrizione in oggetto è frutto dell’utilizzo di:

- Programma 101 del museo Tecnologic@mente.

- Schemi logici Programma 101 originali.

- Data base.

- Simulatore CAD su PC.

Tutta la documentazione, compresi gli schemi logici della macchina tradotta e simulata ed il materiale di supporto, è in formato elettronico e sono disponibili presso il Museo – Laboratorio Tecnologic@mente di Ivrea.

La comprensione di questo documento è facilitata dalla conoscenza e uso dell’insieme della documentazione e del simulatore.

La descrizione riporta diagrammi frutto di simulazione CAD delle funzioni descritte. La macchina simulata è a tutti gli effetti una traduzione 1:1 della P101. La “traduzione” è stata necessaria per adattare la tecnologia, RTL della P101 a quella DTL, del simulatore. Non è stata simulata la logica relativa alle segnalazioni di errore.

La macchina simulata non usando gli stessi componenti logici della P101, comporta differenze implementative, non logiche. La differenza principale tra P101 e Simulatore, è costituita dai comandi dei flip flop. Nella P101 sono utilizzati circuiti derivatori, senza transistor, che commutano il flip flop sul fronte di discesa del segnale. Il simulatore, porte logiche (gate), che operano con il livello.

Per contenere i tempi di esecuzione della simulazione, il simulatore rispetta la sequenza degli eventi ma non i valori assoluti dei tempi della P101. I nomi dei segnali logici, usati nella macchina simulata, hanno la stessa radice di quelli della P101.

La differenza tra logica NOR (P101) e NAND (Simulatore), comporta che la stessa funzione può essere riportata sul diagramma nella forma negata. Il simulatore onde rendere più semplice la lettura del simbolo stampato, utilizza un registro per visualizzarne il codice binario, OU[3:0], non presente nella P101. Per presentare nei diagrammi, dati con parallelismo >1, il simulatore nella radice del nome del segnale scambia una lettera con un valore numerico. Per questo motivo ad esempio il registro:

| P101 | Simulatore |

|---|---|

| HH – HA | H[7:0]. |

| HK – HM | C[2:0]. |

| AA – AF | A[5:0]. |

| ... | ... |

Documentazione tecnica funzionale

La seguente è la documentazione relativa alla famiglia P101, P102, P203, attualmente disponibile in formato elettronico.

- Manuale di programmazione P101

- P102 - P203 Connettore 50 contatti

- P203 Addendum descrizione tecnica

- Fogli logici :

- Fogli Logici P101

- Fogli Logici P102

- Fogli Logici P203

- Legenda dei fogli logici.doc

- Raccolta Circuiti Elettrici.doc

- CAD e Simulatore P101.doc

Documentazione costruttiva

Questa documentazione è struttutata in un database Access (già corredato di query e macro) e dei relativi dati da importare. Il materiale è tutto all’interno della cartella “DB Origine”, e per utilizzarlo occorre seguire le istruzioni descritte nel documento “Introduzione a DB P101”. Nella cartella sono presenti: • File Database per ciacun modello della famiglia Programma 101 • P101.mdb • P102.mdb • P203.mdb • Tabelle di specializzazione prodotto contenenti la lista completa dei generatori segnali: • P101 – T1 Segnali.xls • P102 – T1 Segnali.xls • P203 – T1 Segnali.xls Nota. La descrizione si presta ad una migliore lettura utilizzando un PC, in quanto è possibile effettuare ingrandimenti dei diagrammi, che su carta risultano meno leggibili.

Introduzione

La Programma 101 incorpora nuove esperienze e tradizione Olivetti (Ivrea). Essa nasce nel 1965, dalla integrazione della nascente elettronica con la raffinata meccanica, che al tempo vedeva la prima risiedere nel Laboratori Elettronici di Pregnana Milanese (MI) e la seconda ad Ivrea.

Responsabile del progetto è stato il compianto Ing. Pier Giorgio Perotto, da cui deriva il nomignolo di “perottina”.

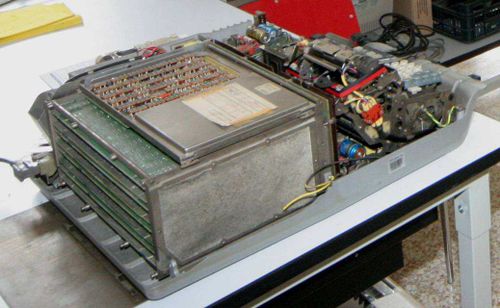

Per comprendere struttura e algoritmi della Programma 101 occorre tenere presenti tecnologia e costi relativi di produzione degli anni 1962-65, periodo del suo progetto. La tecnologia è la RTL, transistor, diodi, resistenze e condensatori non integrati. Nel 1960 , l’Elea primo grande calcolatore a transistor, aveva i componenti montati su piastrini i quali a loro volta inseriti in “pacchi”.

Pacchi e piastrini erano connessi per mezzo di filature.

Nello standard NOR, utilizzato dalla P101, un registro connesso a shift di 8 bit, necessitava di almeno 36 micromoduli con relativi circuiti stampati micro, più: • 16 Micromoduli tipo N20, Flip Flop 16 transistor 48 resistenze • 4 Micromoduli tipo N31, logica di clock ed input dati 4 transistor 12 resistenze • 16 Micromoduli tipo M04, maschere di commutazione Flip Flop 16 diodi 16 condensatori 32 resistori Tenendo presente il prezzo del transistor, si aggirava sulle 1.000 Lire, con il montaggio il costo di produzione del nostro registro (8 bit) si avvicinava allo stipendio mensile di un operaio, 40.000 Lire. Questo spiega la scelta del parallelismo dati (1 bit), l’attenzione estrema all’impiego di ogni transistor comportante l’impiego dello stesso flip flop in fasi e/o funzioni diverse, quali introduzione dati, stampa o cartolina. Quanto sopra si è ottenuto a scapito della linearità e semplicità del progetto. Questa descrizione è frutto della rilettura dei fogli logici originali, da cui si è formato il database e la documentazione costruttiva. Dalla documentazione si è passati alla comprensione degli algoritmi e loro test sul banco di lavoro fornito da simulatore software su personal computer. La descrizione utilizza tabelle e diagrammi, frutto anche degli output derivanti dagli elaborati da Data Base e Simulatore. Le forme d’onda, derivate dall’output del simulatore, rispettano la realtà nella sequenza dei segnali, mentre i tempi sono diversi nei loro valori assoluti.

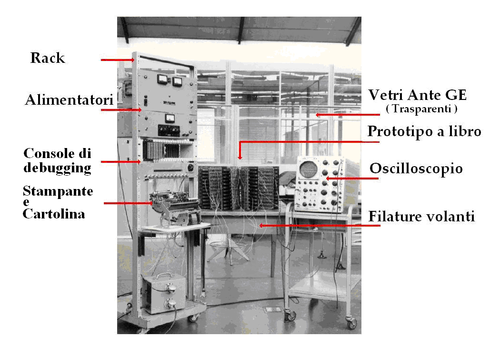

Laboratorio Olivetti di Pregnana Milanese

La Divisione Elettronica dell’Olivetti”, nel 1962 è stata trasferita da Borgolombardo periferia est, a Pregnana Milanese periferia ovest di Milano. All’epoca il laboratorio occupava 400 tra laureati e diplomati e 100 operai. L’età media era attorno ai 25 anni. Erano passati 2 anni da quando l’istituto tecnico Feltrinelli di Milano aveva licenziato i primi periti elettronici italiani. Foto Laboratorio Olivetti di Pregnana Milanese 1963.

La data è fissata dai vetri trasparenti del laboratorio, dopo la vendita della Divisione Elettronica Olivetti alla General Electric, i vetri sono stati colorati con biacca per assicurare riservatezza al progetto. Sono distinguibili: Gruppo piastre elettronico, cablato formato libro, anticipatore della cassettiera. Console debugger con simulatore di tastiera. Prototipo di stampante su striscia. L’oscilloscopio 2 tracce privo di memoria. Manca tester, saldatore, filo e fondamentale stagno. Gli elenchi filature erano prodotti dall’ ELEA 9000, input da schede perforate.

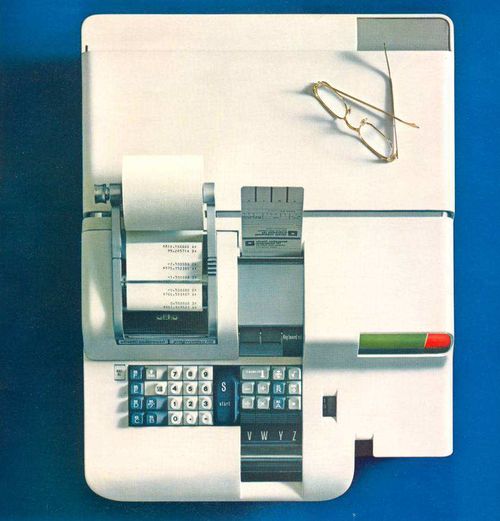

Scheda prodotto

Luogo di progettazione Laboratorio Olivetti – Pregnana Milanese (MI) Italia. Anni 1962 - 1965 Foto P101.

Capo progetto Ing. Pier Giorgio Perotto Designer Mario Bellini del team Sottsass. Carrozzeria in alluminio spessa circa 3 mm. Dimensioni 48x61x19 cm. Peso 29 Kg. Alimentatore 340 Watt. Operabile in modo manuale o da programma. Stampante 30 caratteri al secondo. Cartolina magnetica 120 istruzioni. Registri numerici con 23 cifre. Fino a 15 cifre decimali. Operazioni aritmetiche: Somma. Sottrazione. Moltiplicazione. Divisione. Radice quadrata. Salti assoluti e condizionati

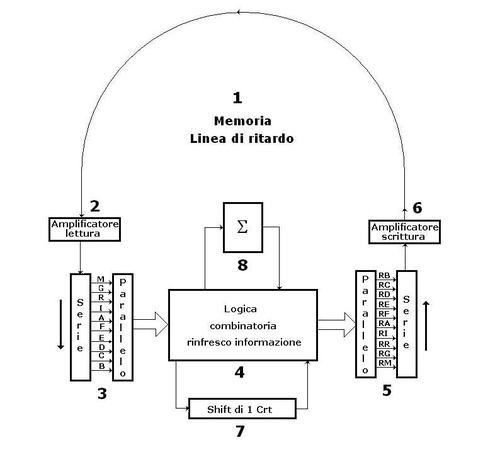

Parte 1. Struttura logica

In Figura 1, lo schema di principio, semplificato, con LDR, registri ed hardware coinvolto nel ciclo di elaborazione dati. Sono evidenziati :

- Memoria sequenziale data da linea di ritardo.

- 10 registri con 24 caratteri di 8 bit. Totale 1920 bit

- Frequenza di 1 Mbit / Sec . Periodo di bit 1 μSec .

- Amplificatore di lettura .

- Messa in parallelo dell’informazione, 1 bit per i 10 registri (10 μSec).

- Logica combinatoria, in caso di macchina in attesa assicura la chiusura dell’anello su cui viaggia l’informazione.

- Serializzazione del bit dei 10 registri.

- Circuito di scrittura \ richiusura dei bit in linea di ritardo.

- Registro shift, 8 bit, contenete 1 Crt da registro (M, A, R) o da sommatore.

- Sommatore serie di 1 bit.

Schema di principio Pogramma 101.

Organizzazione della memoria

La memoria, linea di ritardo costituita da filo di acciaio, è per natura ad accesso sequenziale, parallelismo 1 bit.

La memoria è organizzata in registri (10), dedicati a dati ed istruzioni. I dati su cui opera la macchina sono solo numerici, con segno e virgola naturale. Il registro può contenere un dato di massimo 23 cifre, l’istruzione opera sul contenuto del registro come entità unica, la cifra non è indirizzabile singolarmente. Le istruzioni sono mono carattere, espresse su 8 bit. Il programma attua le scelte tramite una coppia di istruzioni, salto e riferimento relativo. Il riferimento è posto, nella sequenza delle istruzioni, dove il programma riprende l’elaborazione in caso di condizione di salto verificata. Il riferimento è unico specifico per ogni istruzione di salto. La sua ricerca è fatta sequenzialmente a partire dal 1° carattere del 1° registro di programma.

L’individuazione di singole posizioni di carattere, necessarie al processo di esecuzione dell’istruzione, sono adempiute tramite bit di servizio.

Informazione interlacciata

L’acceso all’informazione della Programma 101, dati e programma, essendo la memoria una linea di ritardo è sequenziale. Il tempo di accesso massimo è pari alla lunghezza della linea di ritardo, circa 2,1 mSec.

Lo schema di principio mostra l’hardware, in grado di memorizzare informazione strettamente in forma seriale, 1 bit per registro. Eccezione il registro di shift (7), connesso al sommatore memorizza il carattere ed è indispensabile per assolvere ai compiti di conta e scorrimento relativo di un registro rispetto gli altri.

Il contenuto dei registri è interlacciato a livello di bit. Al 1° bit del 1° registro (B), segue il 1° bit del 2° registro (C) ed a seguire sino al 1° bit del 10° registro (M). La stessa sequenza è mantenuta per tutti i 7 bit sino al completamento del 1° carattere e prosegue dal 2° carattere per gli altri 23.

La capacità hardware di memorizzazione dell’informazione si limita agli 8 bit dei 10 registri interlacciati. L’hardware dedicato alla conta del tempo è ciclico e si limita al carattere singolo. Con un tempo di bit di 1 μsec, il periodo di Crt è quindi, 8*10=80 μSec. ed è realizzato dal registro TA - TH.

Lo schema di principio rappresenta la memorizzazione dei 10 registri. Esso permette la contemporaneità dell’informazione di un bit per registro. Lo schema mostra l’ interlacciamento a livello bit dei registri. Quindi se per 10 μSec ho nei flip flop dei registri l’ 8° bit del 13° Crt, nei 10 μSec precedenti avevo il 7° bit del 13° Crt e nei 10 μSec seguenti avrò il 1° bit del 14° Crt. La temporizzazione si ripete identica per ogni ciclo di LDR. Essa può essere divisa in 3 fasi:

| * Iniziale | Lettura da LDR di 1 bit per registro nel registro serie – parallelo. |

| * Centrale | Elaborazione del bit di registro in logica combinatoria o sommatore, |

| * Finale | Scrittura del bit da logica nel registro parallelo – serie quindi in LDR. |

La parte centrale ha un tempo pari a : 8 bit * 10 Registri * 24 Crt = 1920 μSec. Il tempo totale di attività della temporizzazione comprende quello necessario alle parti iniziali e finali, rispettivamente per la lettura da linea di ritardo del 1° e la scrittura in linea di ritardo del 24° Crt.

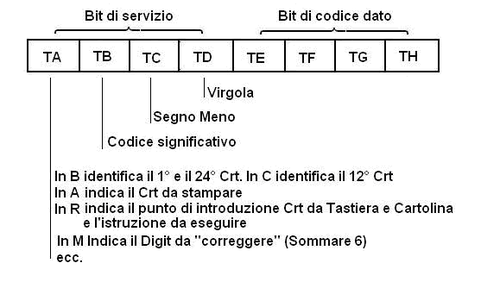

Bit di servizio

I bit di servizio non sono aggiuntivi a quelli dei registri. Essi sono bit dei registri B, C, A, M, R, registri che non possono ospitare istruzioni, dedicati ad uno scopo specifico.

Il registro numerico dispone di 24 caratteri di 8 bit, di cui 23 utili a contenere 23 cifre. La cifra viene espressa dal contenuto dei 4 bit più significativi. I restanti 4 bit, meno significativi, sono disponibili e definiti bit di servizio.

I bit di servizio svolgono funzioni multiple, tra le quali:

- Temporizzazione di base. Inizio e fine dati in linea di ritardo.

- Puntatore carattere. Introduzione dato, esecuzione programma, stampa.

- Specificazione del dato numerico. Dato valido, virgola, segno meno.

- Correzione della cifra BCD.

I bit di servizio della temporizzazione di base, sono scritti nel 1° ciclo di macchina dopo il reset. Essi permangono nella stessa posizione di linea di ritardo, sino allo spegnimento della macchina o tasto di reset.

Negli altri tre casi, i bit di servizio pur mantenendo costante il significato logico, sono mobili all’interno dei 24 caratteri del registro.

Temporizzazione

Per inizializzazione della temporizzazione, si intende la fase che pone nella linea di ritardo, le informazioni necessarie all’ hardware per auto riprodurre le condizioni di operabilità iniziale della macchina.

L’hardware della temporizzazione supporta il trattamento dell’informazione a partire dal bit sino a livello carattere per tutti e 10 i registri. Non esiste hardware dedicato alla conta caratteri.

Il funzione di conta caratteri, nel 1° ciclo dopo il reset, è svolta dal sommatore che essendo libero di altri compiti, indica il tempo di scrittura dei bit di servizio relativi ad inizio e fine linea di ritardo. La conta di 24 caratteri, con un contatore logico di 4 bit, la si compie in 2 cicli. Si sfrutta la fine del 1° ciclo per scrivere, a metà iclo, il bit di servizio indicante inizio di registro dati splittato.

Con i bit di servizio dedicati alla temporizzazione operanti, i cicli di linea di ritardo sono riavviati dal bit di inizio ciclo, che avvia la temporizzazione di bit, la quale senza intervento si ripete all’infinito. Dopo 23 cicli caratteri, viene letto il bit di fine ciclo segnalante la fase di stop, che con la scrittura del 8° bit, 24° carattere del 10° registro (M) ferma la temporizzazione.

Trascorso il tempo di tolleranza (gap), dopo aver percorso tutta la linea di ritardo, il 1° bit di servizio riavvia il ciclo.

13I bit di servizio di avvio e termine temporizzazione, per la loro funzione devono essere posti nel 1° bit del 1° registro (B).

Il bit di servizio per registro splittato è posto nel 1° bit del 2° registro (C).

Questi bit per la loro funzione sono gli unici che possono trovare posto nella posizione di 1° bit del carattere dei 2 registri (B, C).

Puntatore carattere

La necessità di individuazione del punto di lavoro a livello carattere è richiesta durante le operazioni di:

- Introduzione dati o programma da tastiera o cartolina.

- Esecuzione del programma.

- Numero cifre decimali.

- Correzione della cifra BCD.

Allo scopo sono dedicati tre bit di servizio posti nel 1° bit del carattere nei registri (A, R e M). Questi bit sono ovviamente unici nel registro. Il bit del registro è unico A e indica l’ultima cifra decimale. Il bit del registro R è unico e indica l’istruzione da eseguire o il punto di introduzione da tastiera di dati ed istruzioni. I bit del registro M, individuano le cifre da correggere.

L’esigenza di avere tre registri deriva dalle istruzioni di calcolo. Esse in esecuzione programma, hanno contemporaneamente l’esigenza puntare l’istruzione in esecuzione, l’ultima cifra decimale e correzione della cifra BCD.

Avendo lo stesso bit in R, che serve come puntatore di programma ed inserimento carattere da tastiera, ne segue che se si sospende l’esecuzione di un programma per introdurre un dato da tastiera, il punto di inserimento coincide con quello dell’istruzione in corso. Pertanto esso può essere uno tra i 24 disponibili.

Nella esecuzione di somme di due cifre codificate in BCD (Binary Coded Decimal), in caso di riporto, si ottiene la cifra corretta mediante la somma di 6. Questa operazione prende il nome di correzione. La correzione non necessita nelle operazioni di conta, eseguite sempre in binario.

Il bit di servizio utilizzato per segnalare la cifra da correggere è il 1° bit del registro M. Con codice BCD si ha riporto per valori maggiori di 9. A seconda della cifra risultante vi sono due casi:

- Cifra maggiore di 15.

- Cifra compresa tra 10 e 15 inclusi.

La correzione per cifra maggiore di 15, si ha in tutte le istruzioni di calcolo. La correzione per cifra risultante compresa tra 10 e 15, si ha solo nell’esecuzione di istruzioni di somme logiche e moltiplicazioni.

Il riporto di cifra, nel corso di un ciclo di calcolo, può aversi serialmente su più cifre del risultato, a fine ciclo in A saranno presenti tanti bit di correzione quante sono le cifre a cui sommare il 6.

Il sommatore ha capacità di sommare il bit non la cifra, quindi il riporto di cifra si manifesta quando il carattere da correggere è già stato elaborato. La correzione è fatta facendo seguire un ciclo ulteriore per le cifre marcate dal bit di correzione.

Specificazione cifra del dato numerico

La specificazione della cifra utilizza i bit 2°, 3°, 4° del carattere:

| • 2° bit. | Carattere valido. |

| • 3° bit. | Segno meno. |

| • 4° bit. | Virgola. |

Carattere valido è su tutti i caratteri che formano il dato nel registro. Segno meno, dato negativo, su tutti i caratteri che formano il dato nel registro. Virgola, è sempre presente sulla cifra delle unità anche se zero.

La tastiera inserisce le cifre (digit) nei registri della linea di ritardo della in modo naturale a partire dalla cifra più significativa, comprendendo eventualmente virgola e segno meno. Il punto di inserimento delle cifre durante la fase di introduzione del dato da tastiera è fisso, con scorrimento (ritardo), di 1 carattere delle cifre introdotte in precedenza. A fine introduzione dato, la sequenza logica con cui le cifre sono lette, parte dalla meno significativa l’ultima introdotta.

Dato che il punto di inserimento cifra nell’esecuzione di un programma può scorrere, il dato inserito dopo, può trovarsi a cavallo del gap. In questo caso nello stesso ciclo di linea di ritardo, fisicamente alcune cifre più significative precedono, le cifre meno significative che lo concludono.

Da quanto precede segue che manca l’esigenza di indirizzamento all’interno dell’entità logica contenente l’unità elementare di informazione. L’ istruzione e di conseguenza l’hardware provvede ad indirizzare il registro non il carattere.

Struttura dell’informazione

Registro

L’informazione della P101 è strutturata su 10 registri. I registri sono di 24 caratteri (Crt), 8 bit, di cui se dato numerico 23 utili. I registri prendono il nome da una lettera.

L’ordine in cui sono scritti nella linea di ritardo è : B, C, D, E, F, A, I, R, G e M.

Di essi :

| 1. | M | Memorizza i dati da tastiera. |

| 2. | M, A, R | Algoritmi di esecuzione istruzione. |

| 3. | B, C | Deposito dati. Divisibili in due parti di 12 Crt. |

| 4. | D, E, F | Deposito dati o programma. Splittabili se deposito dati o misti. |

| 5. | I, G | Deposito programma. |

I registri deposito dati, tutti o in parte secondo necessità, possono essere raddoppiati (splittati), riducendone la capacità del singolo registro a 12 Crt . L’effetto si ottiene accompagnando il tasto indirizzo con il tasto split (/). La seconda parte del registro, definita splittata, è indirizzata con lettera minuscola, b, c, d, e, f.

La lunghezza di un dato, introdotto da tastiera o risultante dal calcolo, non può superare i 23 Crt nel registro intero o 11 Crt nel registro splittato. I registri sono specializzati per:

- Tipo di informazione. Dati o programma.

- Tipo di utilizzo. Calcolo e/o deposito oppure solo deposito.

- Dimensione. Intero (24 Crt) o Splittato (12 Crt).

Se l’istruzione non contiene l’indirizzo del registro, bit TA – TC = 0, viene selezionato implicitamente il registro M.

Il registro A per la sua funzione in calcolo viene anche detto “accumulatore”.

I registri M, A e R sono richiamati e modificati durante il calcolo in modo implicito.

I registri deposito dati B, C, D, E, F, sono sempre caricati da istruzioni di trasferimento che hanno come indirizzo implicito M o A.

Le istruzioni eseguono il trasferimento, dopo l’allineamento di M ed A, sul 1° Crt se registro intero o sul 13° Crt se splittato. I dati nei registri deposito saranno sempre allineati.

I registri F, E, D, splittati possono contenere promiscuamente dati e programma. I registri G e I non sono selezionabili da programma, essi sono anche indicati come registro programma 1 e 2 e possono contenere solo istruzioni.

Il programma ha disponibili massimo 5 * 24 = 120 istruzioni.

16In introduzione programma, da cartolina o tastiera, i registri di programma sono ad accesso sequenziale e in sequenza fissa a partire da G (1), I (2), F, E , D e sempre a partire dal 1° Crt.

Se il programma è avviato mediante tasto di salto, la prima istruzione eseguita è quella seguente il riferimento corrispondente.

Se il programma viene avviato per la prima volta con il tasto S, la prima istruzione eseguita è quella contenuta nella posizione del primo carattere del registro G. Il registro contenente l’istruzione in esecuzione, cambia a fine esecuzione dell’istruzione nel suo 24° Crt o in seguito dell’esecuzione di una istruzione di salto con riferimento posto in altro registro.

Carattere del registro

I registri A, M, R , B, C possono contenere solo dati.

I registri D, E, F possono contenere sia dati che istruzioni. è la logica del programma a definire il tipo di informazione nel registro.

I registri G (Programma 1), I (Programma 2) possono contenere solo istruzioni.

Il numero indirizzabile di registri dati oggetto di istruzioni, può variare da :

| Minimo | 5 | Registri M, A, R, C ,D | Interi. |

| Massimo | 13 | Registri M, A, R | Interi. |

| Registri B, C, D, E, F, b, c, d, e, f | Splittati. |

Dato

Il Crt è diviso logicamente in due parti :

| TA – TD | Bit di servizio: |

| TA Bit riservato per funzioni sia di sistema che calcolo numerico. | |

| TB Cifra valida. | |

| TC Dato negativo. | |

| TD Cifra accompagnata da virgola. | |

| TE – TH | Bit specificanti la cifra . Peso del bit TE 20 , TF 21 , TG 22 , TH 23 . |

I bit TA e TD o sono assenti o compaiono nel registro su un solo Crt.

Il bit TB compare su tutte le cifre decimali o intere valide.

Il bit TC compare su tutte le cifre se il numero è negativo.

Il bit TD è inserito nella cifra delle unità (10 0 ).

Al reset, i registri M, A e R sono inizializzati con i bit di servizio TA – TD, del 24° Crt = 1.

Si ha il duplice effetto di inizializzare i registri con: • Digit –0. • TA, bit che individua il punto di inserimento dei dati da tastiera o cartolina.

Il trasferimento di un registro deposito in A comporta la scrittura di -0 sul 24° Crt.

I dati in B, C, D, E, F , b, c, d, e, f, registri deposito sono sempre allineati, cifra meno significativa nella 1 a posizione dopo il gap. Se registro splittato cifra meno significativa

nella 13 a posizione dopo il gap.

Tutte le altre cifre seguono senza intervalli.

Essendo i primi 4 bit del Crt di servizio, un Crt contiene una cifra (digit) .

Il dato significativo può avere un numero di cifre variabile, sia totale che decimali.

Il limite massimo è di 23 Crt se registro intero, 11 Crt se registro splittato.

Il numero di cifre decimali può alla fine del calcolo essere massimo di 22.

| Esempio | 9,1234567890123456789012 | totale 23 cifre. |

Il risultato formattato nel registro A, avrà sempre un numero di cifre decimali pari a quanto impostato sulla rotella decimali. Massimo 15.

I dati nei registri, M A o R , in conseguenza delle istruzioni di calcolo scorrono nei registri e alla fine non sono più allineate ai riferimenti iniziali. La posizione finale dipende dall’istruzione e dal valore dei dati.

La natura sequenziale dell’algoritmo di calcolo e del flusso dei dati non richiede di conoscere il peso della cifra. Si deve controllare solo la sua posizione relativa rispetto la virgola.

L’informazione di dato valido, necessaria per iniziare e finire il calcolo, è data da flip flop mantenuti set dalla presenza di bit TB e reset dalla sua assenza.

Si ottiene un effetto “integratore”, forma d’onda a 1 con TB=1, a partire dalla cifra meno significativa, a 0 con TB=0 nel Crt che segue la cifra più significativa.

I flip flop che implementano la funzione dato valido sono tre:

| PM | Registro M. |

| PA | Registro A. |

| TP | Registro dati selezionato dal codice istruzione. |

Istruzione

Le istruzioni, tranne quelle di salto e relativi riferimenti, rispettano tutte lo stesso tipo di codifica.

I primi quattro bit TA – TD, codificano la selezione del registro.

Essendo esclusi dalla selezione i registri I e G dedicati a solo programma, i restanti 8 registri sono selezionati tramite i primi 3 bit TA – TC.

Il quarto bit TD se posto a 1, indica la condizione di split, registro diviso in due.

Nel foglio di programmazione la lettera specificante il registro, indica se:

| Maiuscola | Registro intero o 1 a parte di registro splittato. |

| Minuscola | 2 a parte di registro splittato. |

Tabella codifica indirizzi di selezione registro. Bit TA – TD.

| Registro | HEX | TA | TB | TC | TD |

| M | 0 | 0 | 0 | 0 | 0 |

| C | 1 | 1 | 0 | 0 | 0 |

| R | 2 | 0 | 1 | 0 | 0 |

| D | 3 | 1 | 1 | 0 | 0 |

| A | 4 | 0 | 0 | 1 | 0 |

| B | 5 | 1 | 0 | 1 | 0 |

| F | 6 | 0 | 1 | 1 | 0 |

| E | 7 | 1 | 1 | 1 | 0 |

| / | 8 | 0 | 0 | 0 | 1 |

| c | 9 | 0 | 0 | 0 | 1 |

| R | A | 0 | 1 | 0 | 1 |

| d | B | 1 | 1 | 0 | 1 |

| A | C | 0 | 0 | 1 | 1 |

| b | D | 1 | 0 | 1 | 1 |

| f | E | 0 | 1 | 1 | 1 |

| e | F | 1 | 1 | 1 | 1 |

I secondi quattro bit TE – TF, codificano la selezione della istruzione.

Il codice A esadecimale non è utilizzato.

Tabella codifica istruzioni. Bit TE – TH.

| Istruzione | Tasto | HEX | TE | TF | TG | TH |

| Start | S | 0 | 0 | 0 | 0 | 0 |

| Registro in A | ↓ | 1 | 1 | 0 | 0 | 0 |

| M in registro | ↑ | 2 | 0 | 1 | 0 | 0 |

| Scambio Registro con A | ↕ | 3 | 1 | 1 | 0 | 0 |

| Somma | + | 4 | 0 | 0 | 1 | 0 |

| Sottrazione | - | 5 | 1 | 0 | 1 | 0 |

| Moltiplica | x | 6 | 0 | 1 | 1 | 0 |

| Divisione | : | 7 | 1 | 1 | 1 | 0 |

| Stampa | ◊ | 8 | 0 | 0 | 0 | 1 |

| Azzera Registro | * | 9 | 0 | 0 | 0 | 1 |

| Codice Libero | NU | A | 0 | 1 | 0 | 1 |

| Radice Quadrata | √ | B | 1 | 1 | 0 | 1 |

| Salto V | V | C | 0 | 0 | 1 | 1 |

| Salto W | W | D | 1 | 0 | 1 | 1 |

| Salto Y | Y | E | 0 | 1 | 1 | 1 |

| Salto Z | Z | F | 1 | 1 | 1 | 1 |

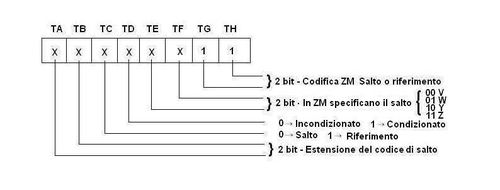

Salto

Le istruzioni di salto utilizzano bit riservati nelle altre istruzioni alla selezione del registro :

| 1. | TA e TB | Estendono i codici riservati ai salti. |

| 2. | TC | Distingue tra salto(0) e riferimento (1). |

| 3. | TD | Distingue tra salto incondizionato (0) o condizionato (1). |

I codici operativi delle istruzioni di salto sono 4, ad essi sono riservati i codici CX, DX, EX

ed FX a cui si fanno corrispondere i tasti V, W, Y e Z.

Il decodificatore in hardware dei salti è ZM.

La condizione da verificare nel salto condizionato, è data dal dato del registro A, esso deve essere positivo, precisamente >0, perché il salto venga eseguito.

I codici di salto utili diventano 16, dato che ogni codice operativo, utilizza i bit TA e TB del Crt, per distinguerne 4 diversi.

Riassumendo si hanno 16 salti incondizionati, 16 condizionati e 16 riferimenti.

Cartolina

La cartolina è il supporto magnetico utilizzato per memorizzare permanentemente i programmi della P101.

La cartolina ha una capacità massima di 5 registri (G, I, F, E, D), 120 Crt di coppie indirizzo – istruzione.

La lettura della cartolina richiede:

- Macchina in stato SA.

- Introduzione di cartolina nel meccanismo di trascinamento.

La scrittura della cartolina richiede:

- Macchina in stato SA.

- Abbassamento del pulsante bistabile AP.

- Introduzione di cartolina nel meccanismo di trascinamento.

L’abbassamento di AP ed AZ, determina la registrazione / lettura di una cartolina corta, 2 registri (E, D), 48 istruzioni. La presenza della cartolina sotto la testina è segnalata da un μswitch (AO).

Il flip flop SO che memorizza lo stato di AO, indica il periodo utile di registrazione/lettura del supporto.

Il flip flop NM, mantiene la sua funzione di pulizia dei registri, la stessa utilizzata per introduzione dati da tastiera, prima di essere settato dal primo ciclo di trasferimento Crt. NM riposiziona il TA di R in TR, cancellando quello precedente. In caso di lettura cartolina, NM tramite XY, blocca la richiusura sulla LDR dei registri G, I, F, E, D azzerandoli.

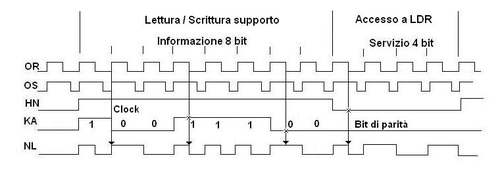

Formato carattere cartolina

Diagramma Formato Crt cartolina.

La cartolina è un supporto di memoria il cui contenuto, fino a 120 Crt, è gestito come stringa di bit unica e continua senza interruzione, sia a livello Crt che registro.

Sorgente o destinazione dei dati, nel nostro caso è la LDR, essa ha un tempo di accesso di 2,1 mSec. Pertanto o si provvede con un registro di supporto o si dedica una parte del supporto stesso allo scopo di fornire il tempo di accesso mancante.

In stampa la stessa esigenza è risolta dal settore privo di denti della ruota fonica, che rendendo disponibile un tempo superiore al tempo di accesso della LDR (2,1 mSec.), garantisce l’ accesso al Crt in LDR in tempo utile.

Per analogia in cartolina, onde ridurre l’hardware, il problema è risolto con l’inserimento di 4 bit supplementari nel Crt.

Ogni Crt di cartolina è quindi composto da 12 bit, 8 informazione e 4 di servizio. 21In totale su ogni pista della cartolina vengono registrati 960 + 480 = 1440 bit.

Sistema di registrazione con ritorno a zero (RZ)

I dati su cartolina vengono registrati utilizzando il sistema di ritorno a zero RZ, esso prevede che ogni periodo di bit abbia almeno una commutazione dovuta al clock.

In registrazione (AP On), il periodo di bit è definito tramite l’oscillatore OR . In ogni periodo di bit si ha la commutazione iniziale di clock, seguita dalla eventuale commutazione a metà periodo in caso di informazione di bit = 1.

In lettura, la prima commutazione magnetica, rilevata dalla testina, viene considerata come clock del 1° bit di informazione. Il clock fa partire il monostabile OS, che ha una durata pari a 2/3 del periodo di bit.

Le commutazioni magnetiche con OS attivo sono considerate come bit 1.

Le commutazioni magnetiche durante OS passivo sono considerate come clock e come tali fanno ripartire OS.

Bit di parità

Diagramma Bit di parità.

L’inserimento dei 4 bit di servizio viene utilizzato per provvedere un bit controllo di parità a livello Crt.

L’informazione da registrare è data da NL, la cui forma d’onda alla fine del Crt (HN), in caso di numero di bit = 1 pari è reset. Se NL è e set, bit dispari, esso viene resettato durante il primo bit di servizio che assume la funzione di bit di controllo della parità.

In lettura, viene controllato che il Crt di 12 bit il numero di bit = 1 sia pari, in caso contrario si attiva la condizione di errore (ER) .

Info su processi fondamentali

L’hardware della Programma 101 non essendo strutturato, rende complicata la lettura dei fogli logici anche per chi desidera una conoscenza non approfondita del suo funzionamento.

Quanto segue vuole fornire alcune informazioni su “processi base”, utili anche per

facilitare un successivo approfondimento dei dettagli.

Introduzione dati

I dati sono di due tipi: numerici ed istruzioni di programma.

Essi possono essere introdotti per mezzo di tastiera e cartolina magnetica. La cartolina tipicamente è utilizzata introdurre il programma.

Dato numerico

Il dato numerico, tipicamente introdotto da tastiera, viene inserito sempre implicitamente nel registro M.

Esso viene battuto in modo naturale, a partire dalla cifra più significativa. Nel caso di numero senza decimali, la virgola è comunque sempre sulla cifra delle unità.

Prima che venga battuta, la virgola accompagna sempre l’ultima cifra introdotta, la sua introduzione ha l’effetto di bloccarne la posizione. L’eventuale cifra seguente costituirà il valore dei decimi di unità.

Il riferimento,TA in R, indica il carattere precedente quello in cui è scritta la cifra attuale, le cifre eventuali precedenti sono spostate in blocco di un carattere per farle posto.

Il segno meno può essere introdotto in qualsiasi momento, a partire da prima battuta, sino a quella che precede il tasto istruzione che chiude la fase dell’introduzione.

A fine introduzione, il dato in M rispetto il riferimento TA in R presenta sul carattere seguente la cifra ultima battuta, la meno significativa, dopo le cifre interposte chiude le cifre quella più significativa. Fisicamente il dato può presentarsi a cavallo del gap, possibile nel caso che il riferimento sia stato spostato dopo l’inizializzazione.

Il dato è sempre visto nella sua interezza, l’informazione di inizio e fine è data da un flip flop che memorizza la persistenza del bit dato valido (TB) nel registro.

Programma

La fase di introduzione del programma, sia da tastiera che da cartolina, parte sempre dal 1° carattere, del registro che memorizza la 1 a istruzione. Il registro sarà G se programma utilizzante 5 registri, E se programma parziale 2 registri.

Le istruzioni successive sono inserite nel registro a seguire a partire dal 2° carattere. I registri seguenti sono interessati a seguito della scrittura nel 24° carattere di quello attuale. La sequenza G, I, F, E, D è bloccata.

Allineamento registri deposito dati

I registri deposito dati sono B, C, D, E, F se interi, b, c, d, e, f se splittati. Le istruzioni operano sui registri dati, splittati o interi, senza differenza. I registri A ed M sono i soli che possono fare scorrere l’informazione in ciclo nei loro 24 caratteri. Lo scorrimento di un carattere è ottenuto , introducendo nel ciclo di richiusura del registro sulla linea di ritardo, il registro K.

L’allineamento del registro A o M, avviene tra il riferimento di inizio registro ed a seconda dell’istruzione in alternativa con cifra più significativa o virgola o cifra meno significativa.

Le istruzioni che scrivono dati nei registri deposito sono solo quelle di trasferimento dal registro M o di scambio con A. Esse fanno precedere la scrittura del dato da una fase di allineamento, che pone la cifra meno significativa nel 1° carattere del registro, se intero, nel 13° carattere se splittato.

Tutte le altre istruzioni che indirizzano un registro deposito, possono leggerlo lasciandolo invariato o cancellarlo.

Calcolo

I registri interessati dalle istruzioni di calcolo sono A, M, R. Il registro A contiene tipicamente, all’inizio dell’istruzione il 1° operando ed alla sua fine il risultato.

Le istruzioni con 2 operandi trasferiscono il registro indicato dall’istruzione in M, 2° operando, prima di eseguire il processo dell’informazione. In caso di radice quadrata, il registro indicato dall’istruzione viene prima trasferito in A poi elaborato.

Tutte le istruzioni di calcolo seguono un processo di cinque fasi in sequenza:

- Collocamento dei dati di inizio calcolo nei registri.

- Allineamento relativo dei registri.

- Scrittura riferimento numero cifre decimali.

- Ciclo di calcolo.

- Formattazione risultato.

L’hardware è in grado di eseguire in un ciclo una somma o sottrazione, tra il dato in A e quello in M. Se l’istruzione richiede cicli multipli come in moltiplicazione, divisione e radice quadrata, conta in R il numero di cicli che costituisce per queste istruzioni il risultato.

L’hardware decide in base all’istruzione e al segno degli operandi, l’esecuzione di un ciclo di somma o sottrazione.

Stampa

La stampante viene utilizzata per:

- Stampa dato e istruzione introdotte da tastiera.

- Istruzioni di stampa.

- Stampa programma.

- Interlinea.

Le diverse stampe e l’interlinea eseguono tutte lo stesso ciclo che comprende:

- Attivazione elettromagnete moto del carrello porta martello.

- Attesa della chiusura micro carrello in moto.

- Attesa da 4 a 28 giri del tamburo – Funzione del dato da stampare.

- Disattivazione elettromagnete moto del carrello porta martello.

- Attesa della apertura micro carrello in moto – Carrello fermo.

La differenza è data dalla eventuale battuta del martello per la stampa di simboli.

La sincronizzazione tra tamburo porta simboli e rotella dentata, ad esempio, il 2° dente si presenta in coincidenza, ogni giro di tamburo, del primo simbolo. Al 16° dente corrisponderà il 16 simbolo, ultimo stampabile prima del gap.

Il gap, la cui durata essendo superiore al tempo di accesso alla linea di ritardo, permette la lettura del codice, istruzione, indirizzo o cifra stampato il giro seguente.

Il codice viene caricato nel sommatore complementato, ad esempio, se si deve stampare il 1° simbolo il codice sarà 0000 (0 Hex), che complementato diventa 1111 (F Hex). Il 1° dente incrementa il sommatore a 0000 (0 Hex), causando il riporto sul 4° bit o riporto di cifra. Ne segue che per stampare il 6° simbolo, codice 0101 ( 5 Hex), con complemento 1010 (A Hex) avrò un riporto sul 4° bit dopo 6 denti.

Onde assorbire le tolleranze introdotte dalla circuiteria di rilevamento del riporto, si sincronizza il comando all’elettromagnete di battuta martello attivandola con la fine del dente che genera il riporto e disattiva con la fine del dente seguente.

Processo dell’informazione - Stati logici

P101- Fogli logici. Foglio 2.

L’elaborazione dell’informazione nell’esecuzione dell’istruzione, è suddivisa in fasi

funzionali denominate stati.

Gli stati sono 15, il nome varia da SA a SS, essi sono tra loro esclusivi e implementati

con flip flop.

La sequenza dei nomi non è sempre indicativa della sequenza di esecuzione.

Sequenza e numero degli stati dipende dalla istruzione e dal modo, manuale o programma. La durata dello stato, misurata in numero di cicli di LDR, è variabile.

Pure variabile è il punto del ciclo in cui avviene la transizione tra stato e stato, tipicamente il gap della linea di ritardo o inizio dell’informazione valida nel registro.

Lo stato di posizionamento all’accensione o reset da tastiera è SE.

Con il reset si inizializzano, temporizzazione (scrittura dei bit di servizio base) e registri M, A ed R con uno zero negativo, dopo tre cicli di linea di ritardo si ha il cambio stato da SE a SA.

Lo stato SA è segnalato dall’accensione della luce verde fissa, in questo stato il sistema è in attesa dell’intervento dell’operatore, sia per calcolo manuale, introduzione cartolina, avvio o prosecuzione del programma.

La fase di attesa intervento dell’operatore termina con la battuta di un tasto istruzione che resetta SA. Lo stato seguente dipende dal codice della istruzione.

Al termine di un calcolo manuale o di esecuzione di un programma, senza errore, si

ritorna sempre allo stato SA con lampada verde accesa fissa.

In caso di errore, si interrompe la sequenza standard degli stati e si forza il ritorno in SA

con lampada rossa accesa fissa.

La fase di lettura o scrittura della cartolina avviene interamente in SA.

Gli stati in genere, sono eseguiti una sola volta per istruzione, tranne le istruzioni di moltiplicazione, divisione e radice quadrata che richiedono l’esecuzione multipla del ciclo di stati SF, SG, SH e SK.

Elenco Stati e loro funzione

Trascurando utilizzi non generalizzabili si elencano in ordine alfabetico gli stati e la funzione che li caratterizza.

SA - Attesa intervento operatore.

Lo stato è raggiunto automaticamente al termine di :

- Fase di inizializzazione (SE).

- Istruzione manuale.

- Esecuzione di un programma.

- Stampa programma.

Lo stato di SA in presenza di lampadino Rosso On, segnala un errore accaduto durante l’esecuzione dell’ultima istruzione. L’errore interrompe la sequenza delle istruzioni e pone la macchina in SA.

La condizione di errore è riposta dall’operatore tramite:

- Battuta di un tasto.

- Introduzione cartolina.

- Reset generale.

Le operazioni sulla cartolina avvengono tutte all’interno dello stato SA. Esse sono caratterizzate dall’impostazione dei pulsanti di modo, AP e AZ, oltre che da SO che segnala presenza di cartolina sotto testina magnetica.

L’ uscita da SA avviene a seguito della battuta di un tasto istruzione , le istruzioni di salto e tasto Start avviano il programma.

SB - Preparatorio all’esecuzione dell’istruzione

SB ha una durata tipica di 2 cicli di LDR. NH = 0 indica 1°giro, NH = 1 2° giro.

In SB, in presenza di una istruzione di salto condizionato, si verifica la condizione, A > 0, prima di passare a SP per l’estrazione dell’istruzione seguente. Il passaggio ad SP avviene comunque se in presenza di salto o riferimento.

Se l’istruzione è di calcolo, tranne radice, avviene il trasferimento del registro indicato nell’istruzione in M , tramite SB * ZA * LX * ZK \ * VX \ . Se radice, il registro con il radicando viene trasferito in A tramite WK * LX, M viene inizializzato con 1 tramite SB * ZK * NH * TR * (TB+TD+TE).

Il diagramma mostra la preparazione nei registri A ed M in caso di radice con registro splittato d.

In A viene trasferito, a partire dal 13° Crt, il numero 1234,7 contenuto in d. Il trasferimento avviene nel 1° giro di LDR.

In M, cancellato nel 1° giro, nel 2° durante TR viene scritto 1.

Diagramma Stato SB. Radice preparazione registri.

Bestand:Prog_101_description-28_1.png

Per le altre istruzioni e un dettaglio maggiore la descrizione è inserita nelle pagine loro dedicate.

SC,SD - Allineamento registri M ed A

SC e SD servono allineare il contenuto di M e A, rispetto il 1° o 13° Crt di LDR.

La cifra da allineare dipende sia dalla istruzione che registro.

Il numero di cicli è variabile, esso incide notevolmente sulla durata dell’esecuzione dell’istruzione, può essere ridotto alternando selezione di registri interi con splittati, in quanto il riferimento per l’allineamento TM, si sposta alternativamente a inizio o metà registro.

L’allineamento avviene per mezzo di uno spostamento relativo del contenuto di un registro rispetto gli altri 9 registri. Lo spostamento si ottiene con l’inserimento di un registro (K) di 1 Crt prima della scrittura in LDR. Si ha quindi il ritardo di 1 Crt per ogni giro di LDR con K connesso.

Quindi il registro M in SC o A in SD, rallenta e scorre all’indietro, avvicinandosi al punto di traguardo (TM) a partire dalla cifra più significativa. Ultima cifra del numero nel registro ad uscire da LDR. Quando la cifra passa oltre il 24° Crt. si trova riscritta sul Crt seguente dell’anello che è il 1° Crt. Il passaggio della cifra più significativa traverso il gap è segnalato dal set di NF, tramite il gate NA*RK*XO.

Il giro seguente le cifre più significative nel registro precederanno quelle meno significative nella lettura della LDR.

Il meccanismo hardware utilizza il flip flop di temporizzazione TM, che in caso di operazioni su registro intero, corrisponde al 24° Crt, se splittato al 12°.

Il Crt su cui si decide l’allineamento è dato dal momento del suo ingresso nel registro K, quindi 1 Crt prima della effettiva scrittura in LDR. A scrittura completata, l’esito è che il dato si trova allineato sul Crt. successivo (1° o 13° Cr).

A seconda dell’istruzione, l’allineamento di M e A avviene su :

- Cifra più significativa. Divisione, radice quadra e se A moltiplica.

- Virgola. Somma algebrica ( + e -) , radice quadra, e se M per moltiplica.

- Cifra meno significativa. Caso di default, per le altre istruzioni.

In caso di istruzioni di calcolo, in caso di una sola cifra per la parte intera, l’allineamento su cifra più significativa coincide con quello sulla virgola.

I due stati SC e SD, sono simili, svolgono le stesse operazioni con oggetto il dato in M e A. Il periodo di osservazione dell’informazione è dato da PO, che definisce il tempo nel quale si leggono cifre valide.

PO in stati diversi da SC e SD è l’or di PM e PA, in SC, PO coincide con PM (M) essendo bloccato PA e in SD con PA (A) essendo bloccato PM.

Il flip flop ND, abilita lo scorrimento del registro attraverso K, esso è settato dal 2° fronte di PO onde evitare lo spezzamento in due tronconi del numero.

Il flip flop NG, in caso di sovrapposizione iniziale di PO a TM, attende che il registro scorra sino ad evitare detta sovrapposizione, quindi abilita con XO il traguardo delle condizioni di allineamento.

Eventuali resti da operazioni precedenti di bit di servizio (TA, TB, TC) “orfani” nel registro, sono cancellati sino alla lettura del 1° bit di cifra o virgola.

Allo scopo ogni TD in TM si mette in moto il duo NA – NB :

| NA | Pone fine con UI1 (NA*XO*RK) che setta NF, al blocco dei bit di servizio “orfani”. |

| NB | Attua con XH1 (NB*CA*NH\) il blocco della scrittura sul Crt seguente dei bit di servizio. |

Il flip flop NH viene settato dai segnali di raggiunto allineamento, i quali sono dati da:

| Gate 02 A 13 | Condizione di cifra più significativa. |

| Gate 02 A 9 | Condizione di virgola. |

| Gate 02 M 1 | Condizione di fine numero. |

Lo scorrere in sequenza dell’informazione dei registri nella LDR, fa si che l’accadimento della prima condizione, se abilitato dalla istruzione, impedisce le altre. Lo stesso vale per la seconda condizione nei confronti della terza.

NH stesso con il giungere del 1° fronte di PO genera YD da cui MS e quindi il cambio stato.

SE - Funzione multiple

SE ha una durata tipica di 2 cicli di LDR. Lo stato di NH = 0 indica 1°giro, NH = 1 2° giro. In inizializzazione,1° stato eseguito, SE dura 3 cicli di LDR.

Le sue funzioni principali sono:

Al Power On, scrive i bit di servizio in B e C che delimitano i confini di LDR e split. Inoltre pone un -0, sul 24° Crt dei registri M, A ed R.

Se istruzione di calcolo, scrive in A il TA che precede la virgola del numero di Crt impostati nella rotella decimali.

Se istruzione di trasferimento lo attua nel suo 2° ciclo.

Per le altre istruzioni ed un dettaglio maggiore la descrizione è inserita nelle pagine ad esse dedicate.

SF,SG,SH,SK,SL - Esecuzione istruzioni di calcolo

Tutti gli stati del gruppo durano 1 ciclo di LDR. Lo stato SL, ultimo del gruppo viene eseguito una sola volta e conclude il calcolo.

SF, SG, SH, SK compongono un ciclo e sono eseguiti in sequenza. In somma e sottrazione il ciclo viene eseguito una sola volta. Nelle altre istruzioni il numero di cicli dipende dal numero di cifre e dal loro valore. In moltiplica l’uscita dal ciclo con il passaggio a SL avviene dopo SK, in divisione e radice dopo SF. In radice il numero di cicli è raddoppiato.

La funzione tipica degli stati nel ciclo di calcolo è:

| SF | Verifica se M > A. |

| SG | Somma 1 al contenuto di R. |

| SH | Esegue la somma algebrica tra M e A. |

| SK | Corregge il risultato della somma algebrica. |

Ogni istruzione di calcolo termina con lo stato SL che ha la funzione di formattarne il risultato.

SM,SN,SS - Riservati alla stampa

La sequenza degli stati di stampa è fissa a SM, segue sempre SN quindi SS. La sequenza è innescata da :

- SA Tutte le istruzioni tranne che di stampa.

- SE Istruzioni di stampa.

- SP Stampa programma (AZ).

Funzione dei singoli stati:

- SM Stampa simbolo istruzione, registro e spazio distanziatore.

- SN Stampa dato numerico.

- SS Attesa del carrello di stampa a riposo.

Con stampa di 30 Crt/Sec. La stampa di un simbolo necessita di 33,33 mSec. Il carrello di stampa è messo e tenuto in movimento da CD, or di SM e SN.

La durata di SM è quasi costante, essendo la variabilità, dovuta al sincronismo tra posizione istantanea del tamburo e comando stampa. Costante è il tempo di 100 mSec. di stampa dei simboli indirizzo, istruzione e spazio. SN ha durata proporzionale al numero di cifre da stampare a cui vanno aggiunti virgola e segno.

SS ha una durata funzione del tempo di ritorno a casa del carrello di stampa indicato dal μswitch AW.

Nel caso di stampa forzata del risultato del calcolo di moltiplicazione, divisione e radice, a seguito della forzatura del codice di stampa A (84H), la sequenza segue la modalità standard.

Unica eccezione, esecuzione da programma dell’istruzione Azzera Registro (*), lo stato SS, segue SE mediante YX ( SE * ZL * HE * HP ). In questo caso l’istruzione non comporta movimento del carrello.

SP - Fetch istruzione di programma

SP ha la funzione di estrarre il codice dell’istruzione da eseguire caricandola nel registro H.

Lo stato SP è raggiunto nei casi di :

- Fine esecuzione istruzione data da YT, se HP = 1 esecuzione programma.

- SB Salto o riferimento di salto.

- SE Istruzione S di start programma.

- SD Stampa programma.

SP ha una durata di 2 - 6 cicli di LDR. Il numero di cicli massimo si ha con il riferimento di salto posizionato nel 5° registro. Se l’istruzione estratta è S (0) si ha il reset di HP, stop all’esecuzione del programma ed il rientro in SA